บทที่ 3 ลักษณะการทำงาน

หน่วยประมงลผล, หน่วยความจำ, และ Flash

หน่วยประมวลผลกลาง

ESP8266EX รวมเอาตัวควบคุมขนาดเล็ก Tensilica L106 32 บิต และ Ultra-low-power RSIC 16 บิต ไว้ด้วยกัน ความเร็วนาฬิกาของ CPU คือ 80 MHz นอกจากนี้ยังสามารถมีค่าสูงสุดได้ที่ 160 MHz ESP8266EX ใช้งานระบบการทำงานแบบเรียลไทม์ (RTOS) ปัจจุบันมีเพียง 20% ของ MIPS ถูกครอบครองโดย Wi-Fi stack ส่วนที่เหลือสามารถใช้งานได้ทั้งหมดสำหรับการเขียนโปรแกรมแอพพลิเคชันสำหรับผู้ใช้และการพัฒนา CPU มีการเชื่อมต่อดังต่อไปนี้

- Programmable RAM/ROM interfaces (iBus) ซึ่งสามารถเชื่อมต่อกับคอนโทรลเลอร์หน่วยความจำและยังสามารถใช้เพื่อเข้าไปดูแฟลช

- Data RAM interface (dBus), ซึ่งสามารถเชื่อมต่อกับคอนโทรลเลอร์หน่วยความจำ

- AHB interface ซึ่งสามารถใช้เพื่อเข้าไปดู register ได้

หน่วยความจำ

ESP8266EX Wi-Fi SoC รวมตัวควบคุมหน่วยความจำและรวมทั้ง SRAM และ ROM MCU สามารถเข้าถึงหน่วยความจำผ่านทางอินเทอร์เฟซ iBus, dBus และ AHB หน่วยความจำทั้งหมดสามารถเข้าถึงได้ตามคำขอขณะที่ตัวตัดสินด้านความจำจะตัดสินใจลำดับการทำงานตามเวลาที่ผู้รับได้รับคำขอเหล่านี้

ตามเวอร์ชันปัจจุบันของ SDK พื้นที่ SRAM ที่มีให้ผู้ใช้มีการกำหนดไว้ด้านล่าง

- ขนาด RAM < 50 kB นั่นคือเมื่อ ESP8266EX ทำงานภายใต้โหมด Station และเชื่อมต่อกับเราเตอร์ พื้นที่ว่างในโปรแกรมที่สามารถเข้าถึงได้ในส่วน heap + data คือ ประมาณ 50 kB

- ไม่มี programmable ROM ใน SoC ดังนั้นโปรแกรมผู้ใช้ต้องเก็บไว้ในแฟลช SPI ภายนอก

Flash ภายนอก

ESP8266EX ใช้แฟลช SPI ภายนอกเพื่อจัดเก็บโปรแกรมของผู้ใช้และรองรับความจุหน่วยความจำได้ถึง 16 MB ในทางทฤษฏี

| OTA | Minimum Flash Memory |

|---|---|

| Disabled | 512 kB |

| Enabled | 1 MB |

AHB and AHB Blocks

AHB Block ทำหน้าที่เป็นตัวตัดสินและควบคุมอินเตอร์เฟส AHB ผ่าน MAC, SDIO (โฮสต์) และ CPU คำขอข้อมูล AHB อาจขึ้นอยู่กับที่หนึ่งในสองของทาส

- APB block

- Flash controller (สำหรับการใช้งานแบบสแตนด์อโลน)

การร้องขอข้อมูลไปยังตัวควบคุมหน่วยความจำมักเป็นคำขอที่มีความเร็วสูงและการร้องขอไปยัง APB Block มักจะเป็นการเข้า register

APB Block ทำหน้าที่เป็นตัวถอดรหัสที่เข้าถึงเฉพาะ programmable registers ภายในบล็อคหลักของ ESP8266EX เท่านั้น APB สามารถไปที่ Radio, SI / SPI, SDIO (โฮสต์), GPIO, UART, RTC, MAC หรือฐานข้อมูลดิจิตอล ขึ้นอยู่กับที่อยู่คำขอนั้นๆ

สัญญาณนาฬิกา

สัญญาณนาฬิกาความถี่สูง

สัญญาณนาฬิกาความถี่สูงใน ESP8266EX ใช้เพื่อขับเคลื่อนทั้งเครื่องรับและส่งสัญญาณนาฬิกา สัญญาณนี้สร้างขึ้นจากเครื่อง crystal oscillator ภายในและ crystal ภายนอก ความถี่ crystal มีตั้งแต่ 24 MHz ถึง 52 MHz

การปรับเทียบภายในเครื่อง crystal oscillator ทำให้มั่นใจได้ว่าสามารถใช้คริสตัลได้หลากหลายความถี่ แต่คุณภาพของcrystal ยังคงเป็นปัจจัยสำคัญในการพิจารณาเกี่ยวกับสัญญาณรบกวนในช่วงเวลาที่เหมาะสมและความไวของ Wi-Fi ที่ดี

| Parameter | Symbol | Min | Max | Unit |

|---|---|---|---|---|

| Frequency | FXO | 24 | 52 | MHz |

| Loading capacitance | CL | - | 32 | pF |

| Motional capacitance | CM | 2 | 6 | pF |

| Series resistance | RS | 0 | 65 | Ω |

| Frequency tolerance | ΔFXO | -15 | 15 | ppm |

| Frequency vs temperature (-25°C ~ 75°C) | ΔFXO, Temp | -15 | 15 | ppm |

ความต้องการสัญญาณนาฬิกาภายนอก

สัญญาณนาฬิกาที่สร้างจากภายนอกสามารถใช้ได้กับความถี่ตั้งแต่ 24 MHz ถึง 52 MHz ลักษณะดังต่อไปนี้คาดว่าจะมีประสิทธิภาพดีเยี่ยมสำหรับความถี่วิทยุ

| Parameter | Symbol | Min | Max | Unit |

|---|---|---|---|---|

| Clock amplitude | VXO | 0.2 | 1 | Vpp |

| External clock accuracy | ΔFXO,EXT | -15 | 15 | ppm |

| Phase noise @1kHz offset, 40 MHz clock | - | - | -120 | dBc/Hz |

| Phase noise @10kHz offset, 40 MHz clock | - | - | -130 | dBc/Hz |

| Phase noise @100kHz offset, 40 MHz clock | - | - | -138 | dBc/Hz |

ความถี่วิทยุ

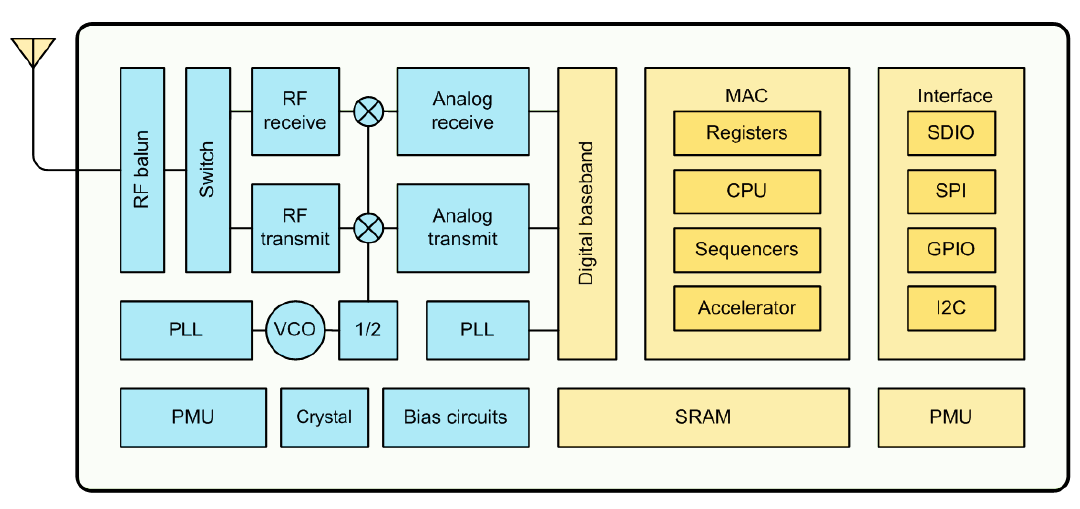

วิทยุ ESP8266EX ประกอบด้วยบล็อกต่อไปนี้

- ตัวรับสัญญาณ 2.4 GHz

- เครื่องส่งสัญญาณ 2.4 GHz

- เครื่องกำเนิดสัญญาณนาฬิกาความเร็วสูงและเครื่อง crystal oscillator

- RTC

- Bias and regulators

- การจัดการพลังงาน

ช่องความถี่

ตัวรับส่งสัญญาณ RF สนับสนุนช่องต่อไปนี้ตามมาตรฐาน IEEE802.11b / g / n

| Channel No. | Frequency (MHz) | Channel No. | Frequency (MHz) |

|---|---|---|---|

| 1 | 2412 | 8 | 2447 |

| 2 | 2417 | 9 | 2452 |

| 3 | 2422 | 10 | 2457 |

| 4 | 2427 | 11 | 2462 |

| 5 | 2432 | 12 | 2467 |

| 6 | 2437 | 13 | 2472 |

| 7 | 2442 | 14 | 2484 |

ตัวรับสัญญาณ 2.4 GHz

ตัวรับสัญญาณ 2.4 GHz แปลงสัญญาณ RF เป็นสัญญาณ quadrature baseband และแปลงเป็นสัญญาณดิจิตอลที่มี ADCs ความเร็วสูง 2 ตัว เพื่อปรับให้เข้ากับสภาพช่องสัญญาณที่แตกต่างกัน ,RF filters, automatic gain control (AGC), DC offset

cancelation circuits และ baseband filters ถูกรวมไว้ภายใน ESP 8266EX

ตัวส่งสัญญาณ 2.4 GHz

เครื่องส่งสัญญาณ 2.4 GHz แปลงสัญญาณ quadrature baseband เป็น 2.4 GHz และขับเคลื่อนเสาอากาศด้วยเครื่องขยายกำลัง CMOS กำลังสูง ฟังก์ชั่นการปรับเทียบแบบดิจิตอลช่วยเพิ่มความเป็นเส้นตรงของเครื่องขยายสัญญาณซึ่งช่วยให้สามารถใช้งานได้โดยเฉลี่ยถึง 19.5 dBm สำหรับการส่งผ่าน 802.11b และ +16 dBm สำหรับการส่งผ่าน 802.11n

เครื่องกำเนิดสัญญาณนาฬิกา

เครื่องกำเนิดสัญญาณนาฬิกาจะสร้างสัญญาณนาฬิกา 2.4 GHz สำหรับเครื่องรับและเครื่องส่งสัญญาณ ส่วนประกอบทั้งหมดของเครื่องกำเนิดไฟฟ้านาฬิกาจะรวมอยู่ในชิปซึ่งรวมถึง inductors, varactors, filters, regulators และ dividers

อินเตอร์เน็ตไร้สาย

Wi-Fi

ESP8266EX ใช้โปรโตคอล TCP / IP, โปรโตคอล WLAN MAC 802.11 b / g / n / e / i และข้อกำหนด Wi-Fi Direct ESP8266EX สนับสนุนแค่การทำงาน basic service set (BSS) ภายใต้ distributed control function (DCF) แต่ยังรวมถึงการทำงานแบบกลุ่ม P2P ที่สอดคล้องกับโปรโตคอล P2P ล่าสุดของ Wi-Fi ฟังก์ชั่นโปรโตคอลระดับต่ำจะถูกจัดการอัตโนมัติโดย ESP8266EX

- RTS/CTS

- acknowledgement

- fragmentation and defragmentation

- aggregation

- frame encapsulation (802.11h/RFC 1042)

- automatic beacon monitoring / scanning, and P2P Wi-Fi direct

การจัดการพลังงาน

ESP8266EX ได้รับการออกแบบด้วยเทคโนโลยีการจัดการพลังงานขั้นสูงและมีไว้สำหรับโทรศัพท์มือถือ, เครื่องใช้ไฟฟ้าที่สวมใส่ได้, และ Internet of Things applications

สถาปัตยกรรมพลังงานต่ำทำงานใน 3 โหมดคือ active mode, sleep mode และ Deep-sleep

mode ESP8266EX ใช้พลังงานประมาณ 20 μA ในโหมด Deep-sleep (RTC กำลังทำงานอยู่) และน้อยกว่า 1.0 mA (DTIM = 3) หรือต่ำกว่า 0.6 mA (DTIM = 10) เพื่อเชื่อมต่อกับ access point

- Off: ขา CHIP_PU อยู่ในระดับต่ำ RTC ถูกปิดใช้งาน register ทั้งหมดจะถูกล้าง

- Deep-sleep: มีเฉพาะ RTC เท่านั้นที่เปิดเครื่อง การกู้คืนหน่วยความจำ RTC สามารถบันทึกข้อมูลการเชื่อมต่อ Wi-Fi พื้นฐานได้

- Sleep: เฉพาะ RTC เท่านั้นที่ใช้งานได้ crystal oscillator ถูกปิดใช้งาน wake-up events ใดๆ (MAC, host, RTC timer, external interrupts) จะทำให้ชิปเข้าสู่โหมด wakeup

- Wakeup: ในสถานะนี้ระบบจะสลับจากสถานะการนอนหลับไปยังโหมด PWR crystal oscillator และ PLLs ถูกเปิดใช้งาน

- On: สัญญาณนาฬิกาความเร็วสูงสามารถใช้งานและส่งไปยังแต่ละบล็อคที่เปิดใช้งานได้โดย register ที่ใช้ในการควบคุมสัญญาณนาฬิกา มีการใช้ lower level clock gating ในระดับ block ซึ่งรวมถึง CPU ที่สามารถปิดกั้นโดยใช้ WAITI instruction ในขณะที่ระบบเปิดอยู่